CMOS邏輯電路因其低功耗、高速度和高集成密度等優(yōu)勢,在現(xiàn)代電子設備中得到了廣泛應用。然而,在高速信號處理和復雜電路環(huán)境中,噪聲問題已成為影響電路性能和可靠性的主要因素。深入分析噪聲的成因并采取有效的優(yōu)化措施,對于提升電路性能和系統(tǒng)穩(wěn)定性至關(guān)重要。

噪聲問題的主要成因

開關(guān)噪聲

開關(guān)噪聲是CMOS邏輯電路中最常見的噪聲問題,通常由輸出開關(guān)速度過快或電路內(nèi)部寄生參數(shù)引起。在開關(guān)過程中,大電流流經(jīng)電感器時會產(chǎn)生電壓尖峰,導致噪聲傳播。這種噪聲可能引發(fā)電路故障或系統(tǒng)不穩(wěn)定。

信號反射

在高速邏輯電路中,傳輸線的特性阻抗與CMOS邏輯電路的I/O阻抗不匹配時,容易發(fā)生信號反射。反射信號可能導致信號延遲、過沖和欠沖,嚴重時甚至會引發(fā)數(shù)據(jù)傳輸錯誤。

串擾

串擾主要發(fā)生在平行傳輸線之間,由電容和電感耦合引起??焖匍_關(guān)信號可能對相鄰電路產(chǎn)生干擾,尤其在高密度布線和高速信號傳輸?shù)碾娐分懈鼮轱@著。

電磁干擾

CMOS邏輯電路在運行過程中會產(chǎn)生電磁場,可能與周圍設備或自身模塊發(fā)生干擾,從而降低系統(tǒng)性能,甚至導致信號完整性問題。

噪聲優(yōu)化的技術(shù)解決方案

提升電源完整性

優(yōu)化電源線和地線的設計是降低開關(guān)噪聲的關(guān)鍵。通過增加電源和地線的寬度、縮短走線長度,可以有效減小寄生電感和電阻,從而平滑電源電壓并抑制噪聲傳播。

實現(xiàn)阻抗匹配

在高速信號傳輸線中,確保傳輸線的特性阻抗與邏輯電路的I/O阻抗匹配是減少信號反射的關(guān)鍵。可以通過在連接器處添加匹配電阻來消除反射干擾。此外,避免急劇彎曲布線以確保信號傳輸?shù)倪B續(xù)性。

優(yōu)化布線設計

為減少串擾噪聲,布線時應增大信號線之間的距離,并盡量縮短平行線的長度。在多層PCB中,采用正交布線并在信號層之間添加接地層,可以有效隔離噪聲。

選擇低噪聲IC

選用具有低噪聲特性的CMOS邏輯IC是解決噪聲問題的有效方法。這類器件通常通過優(yōu)化內(nèi)部電路設計和簡化外圍電路來降低噪聲。

使用濾波與去耦器件

在關(guān)鍵節(jié)點添加低通濾波器可以有效抑制高頻噪聲。同時,應正確處理未使用的輸入引腳,將其連接到電源或地,以避免因未連接而導致的噪聲問題。

加強電磁兼容性設計

在電路設計中加入電磁屏蔽和濾波設計,以減少外部電磁干擾的影響。在系統(tǒng)設計階段,需充分考慮不同模塊之間的電磁兼容性,以優(yōu)化整體電路布局。

案例分析

在某智能設備中,CMOS邏輯電路的高頻信號傳輸因信號反射和串擾問題導致通信誤碼率顯著上升。通過優(yōu)化設計,將布線調(diào)整為扇形,縮小信號線間距,并引入終端匹配電阻,最終成功解決了噪聲問題,顯著提升了信號完整性和通信穩(wěn)定性。

結(jié)論

CMOS邏輯電路中的噪聲問題直接影響電路的性能和可靠性。通過優(yōu)化電路設計、選擇合適的器件以及采用有效的降噪技術(shù),可以顯著提升系統(tǒng)的穩(wěn)定性和抗干擾能力,確保高速、低功耗電子產(chǎn)品的設計質(zhì)量。在復雜的電路環(huán)境中,深入了解噪聲源并采取針對性的解決方案,是實現(xiàn)高效設計的關(guān)鍵。

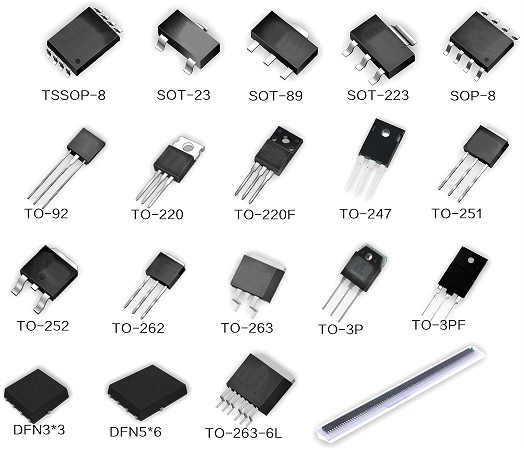

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280