在現(xiàn)代電子設(shè)備中,CMOS邏輯IC的應(yīng)用十分廣泛,其性能的優(yōu)劣對(duì)整個(gè)系統(tǒng)的效率和可靠性有著決定性影響。以下從多個(gè)方面介紹如何通過(guò)優(yōu)化關(guān)鍵因素來(lái)提升CMOS邏輯IC的性能。

一、負(fù)載電容的合理選擇

負(fù)載電容對(duì)CMOS邏輯IC的開(kāi)關(guān)速度和功耗有直接影響。過(guò)大的負(fù)載電容會(huì)降低傳輸速度,增加延遲和功耗,并可能因寄生二極管引發(fā)傳導(dǎo)問(wèn)題。合理選擇負(fù)載電容,可有效降低大電容對(duì)系統(tǒng)的影響,同時(shí)保證正常工作性能。

二、優(yōu)化動(dòng)態(tài)功耗

動(dòng)態(tài)功耗是CMOS邏輯IC功耗的主要來(lái)源之一,可通過(guò)以下方式優(yōu)化:

降低電源電壓 :由于動(dòng)態(tài)功耗與電源電壓的平方成正比,降低工作電壓可顯著降低功耗。

減少負(fù)載電容 :選擇電容值較低的負(fù)載器件,可降低充電和放電過(guò)程中的功耗。

降低開(kāi)關(guān)頻率 :對(duì)于非關(guān)鍵路徑上的信號(hào),適當(dāng)降低頻率可降低動(dòng)態(tài)功耗。

三、低功耗設(shè)計(jì)技術(shù)

在設(shè)計(jì)CMOS邏輯IC時(shí),采用低功耗設(shè)計(jì)技術(shù)可提高整體性能。例如,動(dòng)態(tài)電源管理技術(shù)可根據(jù)實(shí)際工作負(fù)載動(dòng)態(tài)調(diào)整功率,減少不必要的功耗,并將電源釋放給未使用的電路供電。

四、提高信號(hào)完整性

當(dāng)CMOS邏輯IC高速運(yùn)行時(shí),信號(hào)完整性問(wèn)題會(huì)降低性能,可通過(guò)以下方式提高信號(hào)質(zhì)量:

優(yōu)化布線 :減少走線長(zhǎng)度和相互干擾,避免信號(hào)衰減和反射。

添加去耦電容 :在電源和地之間添加去耦電容,減少電源噪聲對(duì)IC的干擾。

增加屏蔽層 :屏蔽關(guān)鍵信號(hào)走線,減少外部噪聲的影響,降低電磁干擾。

五、提高熱性能

隨著CMOS邏輯IC的密度和功率密度的增加,熱管理成為提高性能的重要部分??赏ㄟ^(guò)以下方式實(shí)現(xiàn)散熱優(yōu)化:

使用高導(dǎo)熱率封裝材料 :如陶瓷或金屬外殼,可提高傳熱效率。

添加導(dǎo)熱銅 :在PCB設(shè)計(jì)中添加導(dǎo)熱銅,可增加散熱面積和效率。

采用主動(dòng)散熱裝置 :使用散熱風(fēng)扇或熱管,可顯著改善高功耗時(shí)的溫升問(wèn)題。

六、選擇高性能工藝和器件

選擇高性能CMOS邏輯IC型號(hào)和先進(jìn)制造工藝,可從根本上提高IC性能。例如,選擇高速、低功耗工藝節(jié)點(diǎn)制造的器件,優(yōu)先考慮具有斷電保護(hù)和輸入容限功能的IC型號(hào),以滿足復(fù)雜應(yīng)用場(chǎng)景的需求。

通過(guò)優(yōu)化負(fù)載電容、動(dòng)態(tài)功耗、信號(hào)完整性和熱性能,以及采用低功耗設(shè)計(jì)技術(shù)和高性能器件,可顯著提高CMOS邏輯IC的性能。這些優(yōu)化方法不僅能提升系統(tǒng)性能和效率,還能增加設(shè)備的可靠性和使用壽命。工程師在設(shè)計(jì)過(guò)程中需綜合考慮各種因素,根據(jù)實(shí)際需求合理選擇優(yōu)化方法,以構(gòu)建更高效的電子系統(tǒng)。

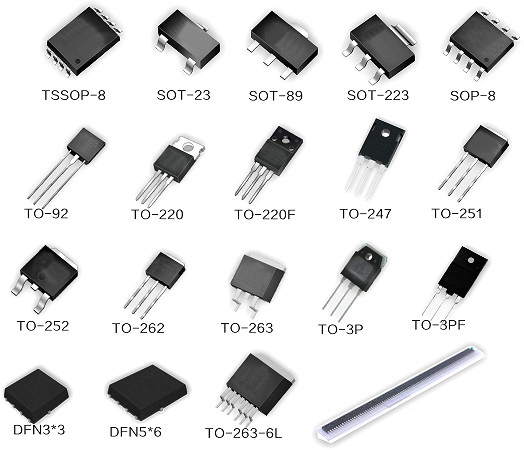

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280